Flip Flop - Módulo 3.2

Electrónica Digital - Circuitos Secuenciales

-

Flip Flop - definição

-

Tipos de Flip Flop

CHANCLAS

Un flip-flop es un circuito electrónico secuencial, con dos estados estables en la salida, que puede utilizarse para almacenar datos binarios.

Básicamente, son similares a los Latches, sin embargo, los Flip-Flops son circuitos secuenciales síncronos, ya que utilizan una señal de reloj en la entrada para sincronizar las salidas.

Nota : Como vimos anteriormente, los Latches se activan por nivel (“0” o “1”) y los Flip-flops por transiciones de reloj (Positivo/Negativo), y esta es una diferencia fundamental entre ellos.

Ambos se utilizan como elementos de almacenamiento de datos.

Los flip-flops se construyen utilizando puertas lógicas, como dos puertas NAND y NOR, o 4 puertas NAND (ver figuras). Cada Flip Flop consta de dos entradas, una señal de reloj y dos salidas, cada una de las cuales es complementaria de la otra.

Tipos de chanclas:

Existen varios tipos de Chanclas, cuyos diseños satisfacen diferentes necesidades. Veremos algunos de ellos en detalle.

Chanclas RS

Chanclas JK

D chanclas

RS Flip-Flop (Reinicio-Configuración)

En el Flip-Flop RS, la entrada “R” Reset o reinicia el dispositivo, generando una salida “0”, y la entrada “S” Set (inicializa), configura el dispositivo o produce la salida “1”.

Las entradas SET y RESET están designadas como S y R.

El símbolo de un RS Flip-Flop se muestra en la figura 1.

El Flip-Flop RS consta de:

- 2 entradas R y S

- 2 Salidas Q y Q' (donde Q' es el complemento de Q)

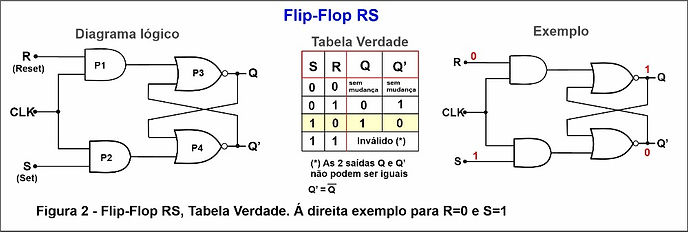

- El Flip-Flop puede estar formado por 2 puertas AND (P1 y P2) y 2 puertas NOR (P3 y P4), con una conexión Cross Loop como se muestra en la figura 2. Son posibles otras configuraciones, con el mismo resultado.

La Figura 2 muestra el Diagrama Lógico y la Tabla de Verdad, así como un ejemplo.

Cómo funciona el Flip-Flop RS

Como tanto R como S pueden ser “0” o “1”, existen 4 posibilidades (siga el Diagrama Lógico y la Tabla de Verdad de la figura 2):

Primera posibilidad de - S=R=0

En este caso, tanto P1 como P2 tienen salida = 0. Dado que P3 y P4 son puertas NOR, entonces, si Q=1 requiere que Q'=0, o, si Q=0 requiere que Q'=1

Según la Tabla de Verdad, las salidas mantienen sus valores anteriores, hasta un nuevo cambio en S o R.

2da Posibilidad - S=1 y R=0

Ahora, P1=0 y P2=1, debido a que la puerta NOR (P4) conduce a Q'=0 y Q=1

3ra Posibilidad - S=0 y R=1

En este caso se produce una inversión del ítem anterior:

Ahora, P1=1 y P2=0, debido a que la puerta NOR (P3) conduce a Q'=1 y Q=0

4ta Posibilidad - S=1 y R=1

Ahora, P1=1 y P2=1.

Como los puertos P3 y P4 son puertas NOR, las salidas serán "0", independientemente del otro puerto. Pero, como las salidas (Q y Q') tienen que ser complementarias, no pueden ser "0" al mismo tiempo, y esta es una condición no válida, como se muestra en la Tabla de Verdad .

Chanclas JK

Características principales de las chanclas JK

• Funciona de manera equivalente a SR, sin embargo, resuelve el problema de incertidumbre cuando S=R=1 en RS Flip-Flop.

• En el Flip-Flop JK no hay estados inválidos, incluso cuando las entradas J y K están configuradas en 1.

• Las salidas del Flip-Flop dependen de la transición del reloj (positiva) (ver figura 3)

Es la más versátil y utilizada entre las Flip-Flops.

La Figura 3 muestra el Símbolo, el Diagrama Lógico y la Tabla de Verdad.

Cómo funciona el flip-flop JK

1ra Posibilidad - J=K=0

Si la entrada J es “0”, entonces P1=0 y Q=1 (Q'=0 por ser complemento)

Si ingresa K=0, P2=0 y Q'=1.

Por tanto, las salidas permanecen en el mismo estado, es decir, sin cambiar el estado del flip-flop.

Es importante destacar que como J y K son “0”, el reloj, sea cual sea, no importa, ya que los puertos P1 y P2 están deshabilitados “0”

2da Posibilidad - J=0 y K=1

Cuando aplicamos un pulso de reloj al flip flop JK, con entradas J=0 y K=1, la salida de la puerta NAND (P1) conectada a la entrada J se vuelve 1. Entonces Q se vuelve 0. Esto restablecerá el Flip - Vuelve al estado anterior.

El Flip Flop estará en estado RESET.

3ra Posibilidad - J=1 y K=0

El análisis es equivalente al anterior, con J=1, K=0 y P2=1. Entonces Q'=0 y el Flip-Flop está en SET

4ta Posibilidad - J=1 y K=1

En este caso, dependiendo del Feedback, no habrá salidas no válidas (Q y Q').

Como se muestra en la Tabla, las salidas cambiarán de un estado a otro.

Flip-Flop JK 74LS76 – ejemplo

El IC 74LS76 es un Flip Flop doble, es decir, tiene 2 Flip Flop JK, en el mismo chip.

La Figura 4 muestra: Distribución de pines, símbolo lógico y tabla de verdad, copiados de la hoja de datos del fabricante. Hay mucha más información (niveles de voltaje, especificaciones físicas, etc.), pero estas son las más relevantes.

Este IC incluye un “Preset, (pin 2) y CLR (Clear pin 3), que se tienen en cuenta en el funcionamiento del Flip Flop, como se muestra en la Tabla de Verdad.

D chanclas

El D Flip-Flop es una alternativa ampliamente utilizada a otros Flip-Flop.

Son ampliamente utilizados en Contadores y Registradores.

Características principales del flip-flop D

Entrada única – Al tener solo una entrada (D), es más sencillo de utilizar.

No hay estados inválidos

Al no tener feedback es más estable que otros tipos de Flip-Flop

Como se puede observar en la figura 5 (Diagrama Lógico y Tabla de Verdad), la salida sólo se ve afectada en la transición positiva del reloj.

Cuando el reloj está en "0", ambas puertas NAND se desactivan , por lo que el estado de D se puede cambiar (a "0" o "1") sin afectar el valor de salida "Q".

Por otro lado, cuando el reloj está alto, ambas puertas NAND están habilitadas . Entonces, cuando hay una transición de reloj positiva, Q se ve obligado a ser igual a D (D=0 Q=0 y D=1 Q=1) .

La Tabla de la Verdad muestra la validez de esta demostración.

Nota : Flip Flop D también puede activarse mediante la transición negativa del reloj. En este caso el diagrama lógico de las puertas es diferente, sin embargo, la Tabla de Verdad sigue siendo válida.

Flip-Flop D 74HC175 - ejemplo

El IC 74HC175 tiene 4 Flip Flop D en el mismo IC

La Figura 6 muestra: Distribución de pines, símbolo lógico y diagrama funcional, copiados de la hoja de datos del fabricante.

El pin MR (Master Reset, pin 1) se usa para restablecer el Flip Flop, y CP (pin 3) es la entrada del Reloj.